## Sixth Semester B.E. Degree Examination, June/July 2019 **Microelectronic Circuits**

Time: 3 hrs.

Max. Marks: 100

Note: Answer any THREE full questions from Part-A and any TWO full questions from Part-B.

PART - A

With a diagram and characteristic curves, derive relationship between  $i_D - V_{DS}$  and discuss the characteristics for an enhancement NMOS transistor. (10 Marks)

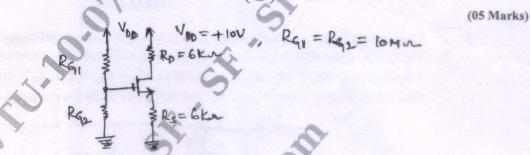

b. Analyze the circuit shown in Fig.Q.1(b) to determine the voltages at all nodes and the currents through all branches. Let  $V_t = 1V$ ,  $K_n^1 \left( \frac{W}{I} \right) = 1 \text{mA} / V^2$  and assume  $\lambda = 0$ .

Fig.Q.1(b)

- Consider a process technology for which  $L_{min} = 0.4 \mu m$ ,  $t_{ox} = 8 n m$ ,  $\mu_n = 450 \text{ cm}^2/\text{v.s}$  and  $V_t = 0.7v,$

- Find Cox and 'k'

- For a MOSFET with W/L =  $8\mu m/0.8\mu m$ , calculate the values of  $V_{GS}$  and  $V_{DSmin}$ needed to operate the transistor in the saturation region with a dc current  $I_D = 100 \mu A$ .

- For the device in (ii), find the value of V<sub>GS</sub> required to cause the device to operate as a  $1000\Omega$  resistor for very small  $V_{DS}$ . (05 Marks)

- Explain the following with the help of a diagram and waveforms:

- i) DC bias point

- ii) Signal current in the drain terminal

- Voltage gain. Derive appropriate equations.

(10 Marks)

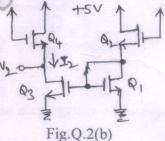

b. For the devices in the circuit of Fig.Q.2(b),  $|V_t| = 1v$ ,  $\lambda = 0$ ,  $\gamma = 0$ ,  $\mu_n C_{ox} = 50 \mu A/v^2$ ,  $L = 1 \mu m$ ,  $w = 10 \mu m$ , find  $V_2$  and  $I_2$ . How do these values change if  $Q_3$  and  $Q_4$  are made to have  $W = 100 \mu m$ ? (05 Marks)

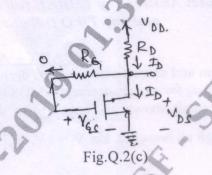

Using the feedback bias arrangement shown in Fig.Q.2(c) with a, 9V supply and NMOS device for which  $V_t = 1v$ ,  $K_n^1 \left( \frac{W}{L} \right) = 0.4 \text{mA} / v^2$ , find  $R_D$  to establish a drain current of 0.2mA. If resistor values are limited to those on the 5% resistor scale, what value would you choose? What values of current and VD result?

a. Discuss the IC biasing techniques with relevant diagrams and expressions. (10 Marks)

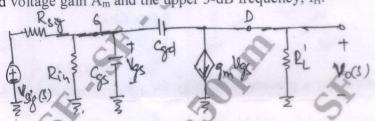

Fig.Q.3(b) shows the high-frequency equivalent circuit of a common source MOSFET amplifier. For  $R_{\text{sig}}=100\text{K}\Omega$ ,  $R_{\text{in}}=420\text{K}\Omega$ ,  $C_{\text{gs}}=C_{\text{gd}}=1\text{pf}$ ,  $g_{\text{m}}=4\text{mA/v}$ ,  $R_{\text{L}}^{1}=3.33\text{K}\Omega$ , find the mid band voltage gain Am and the upper 3-dB frequency, f<sub>H</sub>. (06 Marks)

With an equivalent circuit discuss Miller's theorem.

(04 Marks)

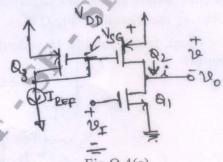

A CMOS common-source amplifier shown in Fig.Q.4(a) has  $W/L = 7.2 \mu m/0.36 \mu m$  for all transistors,  $\mu_n$   $C_{ox} = 387$   $\mu A/v^2$ ,  $\mu_p$   $C_{ox} = 86$   $\mu A/v^2$ ,  $I_{REF} = 100 \mu A$ ,  $V_{An}^1 = 5 v / \mu m$ ,  $\left|V_{AP}^{1}\right|=6V/\mu m$ . For  $Q_{1}$ ,  $C_{gs}=20 fF$ ,  $C_{gd}=5 fF$ ,  $C_{L}=25 fF$ ,  $R_{sig}=10 K\Omega$ . Assume  $C_{L}$  includes all capacitances of Q2 at the output mode. Find fH using Miller equivalence and the open circuit time constants. Also determine the exact values of fp1, fp2 and fz and hence provide (09 Marks) another estimate for fH.

Fig.Q.4(a)

b. Derive an expression for voltage gain and high frequency response of CG amplifier with (08 Marks) active loads.

Discuss the bipolar mirror with base-current compensation.

(03 Marks)

- 5 a. With diagram, derive an expression for input offset voltage of the differential pair. (07 Marks)

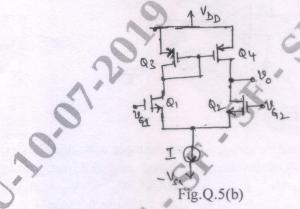

- b. Consider an active-loaded MOS differential amplifier shown in Fig.Q.5(b). Assume for all transistors,  $\frac{W}{L} = 8.2 \mu m / 0.36 \mu m$ ,  $C_{gs} = 20 f F$ ,  $C_{gd} = 5 f F$ ,  $C_{db} = 5$  fF. Let  $\mu_n$   $C_{ox} = 387$   $\mu A/v^2$ ,  $\mu_p$   $C_{ox} = 86$   $\mu A/v^2$ ,  $V_{An}^1 = 5 v / \mu m$ ,  $\left|V_{Ap}^1\right| = 6 v / \mu m$ . Bias current I = 0.2 m A,  $R_{ss} = 25 K \Omega$ ,

$C_{ss} = 0.2PF$  and the capacitance at output node  $C_x = 25fF$ . Determine the low-frequency values of  $A_d$ ,  $A_{cm}$  and CMRR. Also find the poles and zero of  $A_d$  and the dominant pole of CMRR.

c. With a diagram, explain the two-stage CMOS OPAmp.

(04 Marks)

## PART - B

6 a. Explain the properties of negative feedback.

(08 Marks)

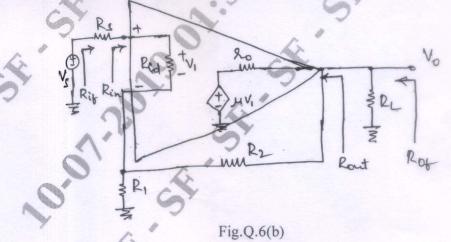

b. For the OpAmp circuit shown in Fig.Q.6(b),  $\mu = 10^4$ ,  $R_{id} = 100 K\Omega$ ,  $r_0 = 1 k\Omega$ ,  $R_L = 2 K\Omega$ ,  $R_1 = 1 K\Omega$ ,  $R_2 = 1 M\Omega$  and  $R_s = 10 K\Omega$ . Find the values for A,  $\beta$ , the closed – loop gain  $(v_0/v_s)$ , input resistance  $(R_{in})$  and the output resistance  $(R_{out})$ .

c. Discuss the effect of feedback on the amplifier with two-pole response.

(05 Marks)

- 7 a. Discuss and derive an expression for output voltage of antilogarithmic amplifiers. (05 Marks)

- b. With a diagram, derive an expression for common mode gain of single Op-Amp difference amplifier.

(07 Marks)

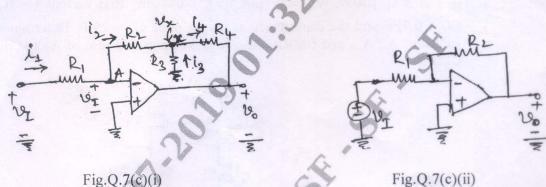

c. Assuming OpAmp to be ideal, derive an expression for closed-loop gain  $(v_0/v_I)$  of the circuit shown in Fig.Q.7(c)(i). Using this circuit design an inverting amplifier with a gain of 100, input resistance of  $1M\Omega$ . For practical reasons, not to use the resistors greater than  $1M\Omega$ . Compare your design with the circuit shown in Fig.Q.7(c)(ii). (08 Marks)

- 8 a. Explain the transistor sizing with an example of 4 input NAND gate. (06 Marks)

- b. Consider a CMOS inverter fabricated in a 0.25  $\mu m$  process for which  $C_{ox}=6 f F/\mu m^2$ ,  $\mu n$   $C_{ox}=115 \mu A/v^2$ ,  $\mu_p C_{ox}=30 \mu A/v^2$ ,  $V_{in}=-V_{tp}=0.4 V$ ,  $V_{DD}=2.5 V$ . W/L ratio for  $Q_N=0.375~\mu m/0.25 \mu m$  and for  $Q_P=1.125 \mu m/0.25 \mu m$ ,  $C_{gs}=C_{gd}=0.3 f F/\mu m$  of gate width,  $C_{dbh}=1 f F$ ,  $C_{dbp}=1 f F$  and  $C_w=0.2 f F$ . Find  $t_{PHL}$ ,  $t_{PLH}$  and  $t_P$ . (07 Marks)

- c. Explain the parameters used to characterize the operation and performance of logic family.

(07 Marks)